# Elimination of the Sidewall Defects in Selective Epitaxial Growth (SEG) of Silicon for a Dielectric Isolation Technology

John M. Sherman, Gerold W. Neudeck, Fellow, IEEE, John P. Denton, Member, IEEE, Rashid Bashir, Member, IEEE, and William W. Fultz, Associate Member, IEEE

Abstract—Selective epitaxial growth (SEG) of silicon has not had widespread use as a dielectric isolation technology due to the near sidewall defects at the  $\mathrm{SiO}_2$  silicon interface. These defects are located in the first 1–2  $\mu \mathrm{m}$  of the SEG/sidewall  $\mathrm{SiO}_2$  interface. Diode junctions intersecting the sidewall and 5  $\mu \mathrm{m}$  removed from the sidewall were fabricated in SEG material using thermally grown silicon dioxide (OX) and thermally nitrided thermal silicon dioxide (NOX) as the field insulating mask. Averaged over 16 devices of each type, diodes fabricated with NOX had much better low current I-V characteristics and minimum ideality factors (1.03) than diodes fabricated with OX field oxides (1.23). Junctions intersecting the NOX field insulator had nearly identical characteristics to bulk SEG.

### I. INTRODUCTION

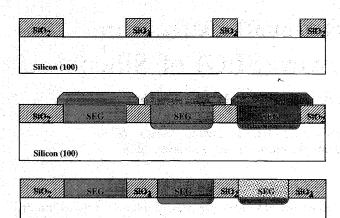

RESENTLY the main emphasis is producing smaller devices with less parasitic capacitance, that switch faster, and have increased packing densities. Trench and local oxidation of silicon (LOCOS), for the next generation of ULSI, have a number of drawbacks as device dimensions are further reduced. LOCOS has lateral oxidation or the bird's beak which reduces the active area and results in a nonplanar surface. In the case of CMOS, latch-up and cross-talk prevention requires larger spacing between MOSFET's. In the 1980's, the use of selective epitaxial growth (SEG) was proposed as a dielectric isolation technology that had a higher packing density [1], [2], eliminated the bird's beak, had no pad oxide or deposited nitride, and required no additional oxidation steps. As illustrated in Fig. 1, fabricating CMOS with SEG, up to the point where the N- and P-channel devices are produced, is a much simpler process than LOCOS. The wafer is first thermally oxidized (SiO<sub>2</sub>), then patterned for the device areas, the oxide is etched, and then SEG is grown to slightly above the oxide. Chemical mechanical polishing (CMP) of the SEG, back to the local area field SiO<sub>2</sub> etch stop, provides a planar surface and removes all facets. The greatest barrier to wide spread use of SEG as an isolation technology and in the fabrication of small devices was the sidewall electronic quality. Devices fabricated in SEG material were measured to be as good as substrate devices only when all junctions were  $1-2~\mu m$  from the sidewall [3]–[5]. When the junction intersected the sidewall, the low current I-V characteristics became degraded, with large leakage currents [4], [6], [7], lower breakdown voltages [1], and larger junction ideality factors. These defects have recently been determined to be due to stresses induced in the SEG during cool-down from the growth temperature. The large mismatch in the thermal expansion coefficients of silicon and the field  $SiO_2$  was shown to be the cause [9], [10]. This paper reports for the first time a fabrication process for the near elimination of these sidewall defects in SEG and hence makes new device structures and a compact isolation technology possible.

# II. DIODE FABRICATION

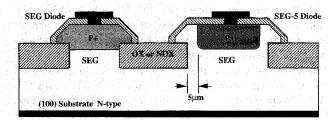

nitrided thermal silicon dioxide (NOX) Thermally was used as the field insulator to reduce the differences (SiO<sub>2</sub> < Si < Si<sub>3</sub>N<sub>4</sub>) in the relative expansion coefficients between silicon and  $SiO_2(C_{T.Si} = 5.8 \times 10^{-6}/C, C_{T.SiO_2} =$  $5.0 \times 10^{-7}$ /°C). Since Si<sub>3</sub>N<sub>4</sub> has a larger  $C_T$  than silicon, a nitrided SiO<sub>2</sub> should have a closer match. The field oxide was formed on (100) silicon wafers using a dry O2 at 1100°C for 2 h and then 10 min in steam to obtain 0.9  $\mu$ m SiO<sub>2</sub> (OX). The NOX film was obtained by thermally nitriding the above SiO<sub>2</sub> in pure ammonia (NH<sub>3</sub>) at 1100°C for 60 min. At this temperature, nitrogen is incorporated into the oxide and the thermal expansion coefficient is modified. After nitridation, SIMS profiles indicated it contained ~2-4 atm% of nitrogen [11], [12]. For defect comparison, both OX and NOX were used as the field dielectric. Fig. 2 illustrates the two types of diodes fabricated to measure the differences in sidewall defects. Note that one has a junction that intersects the sidewall (SEG) and the other is  $5 \mu m$  from the wall (SEG-5). Seed windows for SEG were RIE or wet etched into both OX and the NOX wafers. RIE consisted of a 200 W, 80 mTorr, CHF<sub>3</sub> plasma etch followed by a 5 min, 1000°C steam oxidation to remove any damage. The wafers were dipped in BHF for 30 s to remove the native oxide and then n-type SEG was grown at 970°C, 40 Torr, with gas flows of  $SiH_2Cl_2 = 0.22$  slpm, HCl = 0.56 slpm,  $H_2 = 60$  slpm in a commercial CVD reactor with a growth rate of about

Manuscript received October 24, 1995; revised February 23, 1996. This work was supported by SRC 95-SJ-108 and by Delco Electronics.

J. M. Sherman was with the Purdue University, School of Electrical and Computer Engineering, West Lafayette, IN 47907 USA. He is now with Intel Corporation, Albuquerque, NM 87114 USA.

G. W. Neudeck and J. P. Denton are with Purdue University, School of Electrical and Computer Engineering, W. Lafayette, IN 47907 USA.

R. Bashir is with National Semiconductor, Santa Clara, CA 95052 USA.

W. W. Fultz is with Delco Electronics, Kokomo, IN 46902 USA.

Publisher Item Identifier S 0741-3106(96)04495-3.

Silicon (100)

Fig. 1. Cross section of SEG as a dielectric isolation technology.

Fig. 2. Cross section of diodes where the junction intersects the sidewall (SEG) and diodes that have the junction 5  $\mu$ m from the wall (SEG-5).

$0.12 \,\mu\text{m/min}$ . Boron was implanted at an energy of 25 keV with a dose of  $1 \times 10^{14} \,\mathrm{cm}^2$  to create the  $p^+$  regions, followed by a 10 min 1000°C anneal and then a Al-1%Si metallization step. A hydrogen anneal was then performed for 20 min at 475°C.

### III. EXPERIMENTAL RESULTS

Diode I-V and ideality factors were measured for each type of diode and each dielectric with a HP 4145B parameter analyzer. A total of 144 diodes, that had a range of areas and perimeters (16 devices), were measured. Diodes fabricated in the substrate, as process control devices, had an average minimum ideality factor (n) of 1.02 as listed in Table I. Those SEG diodes with wet etched thermal oxide (OX) as the insulator mask had excellent low current characteristics when the junction was  $5 \mu m$  from the sidewall (OXSEG-5) with the average minimum ideality factor of near 1.00. When the junction intersected the SiO<sub>2</sub> sidewall (OXSEG), the average minimum ideality factor increased to 1.23 and the recombination currents increased significantly.

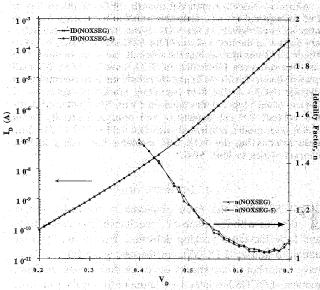

Diodes fabricated with NOX as the dielectric also showed excellent characteristics when the junction was at least 5  $\mu$ m from the sidewall (NOXSEG-5) with the average minimum ideality factor of 1.03. Now, however, when the junction intersected the NOX sidewall (NOXSEG), the device I-V characteristics remained nearly the same and the average minimum ideality factor was essentially the same at 1.03. The I-V characteristics are shown in Fig. 3 for a typical NOXSEG and a NOXSEG-5 device with the same area and perimeter,

TABLE I Average\* Minimum Ideality Factor of SEG DIODES WITH WET AND DRY ETCHED SEED WINDOWS

|   |                   | 1,046 1,080,000 | <u> </u>      | <u>ni roja M. Isli wakazi (j. 181</u> 6) |

|---|-------------------|-----------------|---------------|------------------------------------------|

|   | Insulator<br>Type | Diode Type      | Seed Wet Etch | Seed Dry Etch                            |

| 2 | N/A               | Sübstrate       | 1.02*         | N/A                                      |

|   | Thermal Oxide     | OXSEG-5         | 1.00          | 1.02                                     |

|   | Thermal Oxide     | OXSEG           | 1.23          | 1.10                                     |

|   | Nitrided Oxide    | NOXSEG-5        | 1.03          | 1.15                                     |

|   | Nitrided Oxide    | NOXSEG          | 1.03          | 1.08                                     |

\* 16 diodes of each type of each kind

Fig. 3. I-V characteristics and ideality factor characteristics for NOXSEG and NOXSEG-5 diodes with wet etched seed windows.

indicating how closely they are matched, particularly in the low current region. Similar results were obtained for dry etched seed windows as shown in Table I where the diodes intersecting the sidewall were even a little better than the nonintersecting diodes.

#### Samuel Sail Selection of the sail and the sail sails IV. CONCLUSIONS

valence active so.

Diodes whose junctions intersected the SEG/thermally nitrided oxide sidewall showed nearly identical electrical characteristics to those  $5 \mu m$  away from the wall and were very comparable to substrate devices and to the OXSEG-5 devices. Sidewall defects produced in SEG of silicon were essentially reduced to bulk levels, within experimental error, using a thermally nitrided thermal oxide as the field insulator, which in turn becomes the dielectric for a trench-like isolation technology. The drastic reduction in the sidewall defects is a result of the reduced stress placed on the SEG upon cool-down from the growth temperature.

## REFERENCES

[1] N. Endo, K. Tanno, A. Ishitani, Y. Kurogi, and H. Tsuya, "Novel device isolation technology with selective epitaxial growth," IEEE Trans. Electron Devices, vol. ED-31, pp. 1283-1288, 1984.

Appell Septim of Asia

- [2] N. Kasai, N. Endo, A. Ishitani, and H. Kitajima, "1/4 μm isolation technique using selective epitaxy," *IEEE Trans. Electron Devices*, vol. ED-34, no. 6, June 1987.

- [3] J. W. Siekkinen, G. W. Neudeck, W. A. Klaasen, "Fabrication results of selective epitaxial growth silicon bipolar transistors for material and device characterization," *IEEE Trans. Electron Devices*, vol. ED-35, no. 10, pp. 1640-1644, Oct. 1988.

- 10, pp. 1640-1644, Oct. 1988.

[4] W. E. Klaasen and G. W. Neudeck, "Sidewall gate controlled diode for the measurement of silicon selective epitaxial growth-SiO<sub>2</sub> interface defects," *IEEE Trans. Electron Devices*, vol. 37, no. 1, pp. 273-279, Jan. 1990

- [5] G. W. Neudeck, P. J. Schubert, J. L. Glenn, J. A. Friedrich, W. A. Klaasen, R. P. Zingg, and J. P. Denton, "Three dimensional devices fabricated by silicon lateral overgrowth" *J. Electron. Mat.*, vol. 19, no. 10, pp. 1111-1117, Oct. 1990

- [6] P. Gilbert, G. Neudeck, J. Denton, and S. Duey," Quasi-dielectric isolated bipolar junction transistor with sub-collector fabricated using selective epitaxial growth," *IEEE Trans. Electron Devices*, vol. 38, no. 7, pp. 1660-1665, July 1991.

- [7] S. M. Sze, Physics of Semiconductor Devices. New York: Wiley, 1981.

[8] J. A. Friedrich and G. W. Neudeck, "Interface characterization of silicon

- [8] J. A. Friedrich and G. W. Neudeck, "Interface characterization of silicon epitaxial lateral growth over existing SiO<sub>2</sub> for 3-dimensional CMOS structures," *IEEE Electron Device Lett.*, vol. 10, no. 4, pp. 144–164, Apr. 1989.

- [9] R. Bashir, G. W. Neudeck, Y. Haw, and E. P. Kvam, "Characterization and modeling of sidewall defects in selective epitaxial growth of silicon," J. Vac. Sci. Technol., vol. 13, no. 3, pp. 928-935, June 1995.

[10] R. Bashir, G. W. Neudeck, Y. Haw, and E. P. Kvam, "Characterization

- [10] R. Bashir, G. W. Neudeck, Y. Haw, and E. P. Kvam, "Characterization and modeling of sidewall defects in selective epitaxial growth of silicon," J. Vac. Sci. Technol., vol. 13, no. 3, pp. 928-935, June 1995.

- silicon," J. Vac. Sci. Technol., vol. 13, no. 3, pp. 928–935, June 1995.

[11] W. W. Fultz and G. W. Neudeck, "A nitrided oxide dielectric for epitaxial lateral overgrowth applications," School of Electrical Engineering, Purdue University, West Lafayette, IN, Tech. Rep. TR-EE 95-4, Jan. 1994

- [12] R. Bashir, S. Kim, N. Qadri, D. Jin, G. W. Neudeck, J. P. Denton, G. Yeric, K. Wu, and A. Tacsh "Degradation of insulators in the silicon SEG ambient," *IEEE Electron Device Lett.*, vol. 16, no. 9, pp. 382–384, Sept. 1995.