# Characterization of sidewall defects in selective epitaxial growth of silicon

#### R. Bashir

National Semiconductors, Santa Clara, California 95052

## G. W. Neudeck

School of Electrical Engineering, Purdue University, West Lafayette, Indiana 47906

#### Y. Haw and E. P. Kvam

School of Materials Engineering, Purdue University, West Lafayette, Indiana 47906

## J. P. Denton

School of Electrical Engineering, Purdue University, West Lafayette, Indiana 47906

(Received 1 December 1994; accepted 28 March 1995)

The sidewall defects in high quality selective epitaxial growth (SEG) of silicon were characterized. Three different SEG diode structures were fabricated and the bulk and perimeter defects were characterized through electrical measurements and transmission electron microscopy (TEM). The structures investigated were SEG grown in a 1.2  $\mu$ m thick wet-etched field oxide, SEG grown in 1.2  $\mu$ m thick reactive-ion etched field oxide, and SEG grown in a 1.2  $\mu$ m high and 0.3  $\mu$ m wide sidewall oxide cavity. The thin sidewall oxide cavity SEG diode showed the best ideality factors and minimum saturation current densities for diodes intersecting the sidewall, indicating the least thermal stress generated at the SEG/oxide sidewall interface during the cool-down period. Cross-sectional TEM micrographs showed no defects in the bulk SEG or at the sidewall, indicating that the thermal stress in all the processes was not high enough to cause plastic deformation, dislocations, or stacking faults. © 1995 American Vacuum Society.

## I. INTRODUCTION

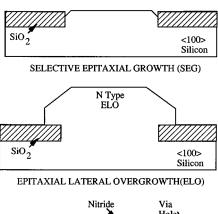

Selective epitaxial growth (SEG) of silicon has been identified as a key technology for the next generation very large scale integrated/ultralarge scale integrated circuits (VLSI/ ULSI) which will use novel three-dimensional bipolar, metal oxide semiconductor, bipolar-complementary metal oxide semiconductor, and silicon-on-insulator (MOS, BiCMOS, and SOI) devices. 1,2 SEG and related selective growth techniques such as epitaxial lateral overgrowth (ELO) and confined lateral selective epitaxial growth (CLSEG) have been used to fabricate novel three-dimensional devices.<sup>3–7</sup> (See Fig. 1.) The bulk SEG silicon material is of excellent quality but the material close to the sidewall insulator can have a high defect density. Various authors have reported the presence of defects along the sidewall.<sup>8-10</sup> A factor of 10-100 increase in leakage currents has been reported when the junctions intersect the SEG sidewall. The presence of the sidewall defect is considered to be the single most important problem hindering the widespread use of SEG in semiconductor processing because junctions and depletion regions intersecting these sidewall defects will result in undesirable recombination-generation currents. Hence, it is extremely important that these defects need to be characterized and eliminated.

It is postulated that the main cause of the SEG/ELO side-wall defects is thermal stress after the SEG growth during the cool-down period. The oxide /silicon interface is a location of high internal strain. As a strain relief mechanism, stacking faults could be generated in the silicon material. The strain could be introduced as a result of the difference in thermal coefficient of expansion between the silicon overgrowth and the oxide. At high temperatures, the silicon yield strength is lowered and the thermal stress could exceed the

material yield strength. If this situation occurs, the internal stress will be relieved by plastic deformation of silicon. <sup>10,11</sup> Some practical steps have been suggested to reduce the internal strain introduced by the Si overgrowth. <sup>10</sup> The insulating film could be made thinner, which would reduce the internal strain. The thermal stress could also be reduced if the thermal coefficient of expansion of the insulator next to the overgrowth is matched to that of silicon. However, the very limited choices of insulator do not allow the matching of expansion coefficients. The reduction in growth temperature itself should reduce the stress and strain developed in the material, at the expense of slower growth rates.

It is the purpose of this paper to characterize the sidewall defects in selective epitaxial growth of silicon. By the fabrication of a unique structure, it is shown that the quality of the SEG/oxide sidewall interface can be greatly improved by using a thin sidewall oxide. The results are attributed to a lower thermal stress in the thin sidewall oxide cavity SEG structure. The material quality was electrically characterized by fabricating diodes using selective epitaxial growth and chemical-mechanical polishing with junctions intersecting the sidewall interface of interest. Bulk and perimeter ideality factors and saturation current densities were extracted to characterize the bulk and sidewall SEG material.

# **II. CHARACTERIZATION TECHNIQUE**

The current through a diode in the forward bias region is the sum of a diffusion component and a recombination current. The recombination current is characterized by the ideality factor  $\eta$ , theoretically equal to 2. The recombination current is dominant at low forward biased applied voltages while the diffusion current dominates at higher voltages. The

GROWTH (CLSEG)

Fig. 1. Various selective silicon growth techniques.

diffusion and recombination current can be lumped together, and the perimeter current component can be included to obtain the total diode current:

$$I = AJ_{b0} \left[ \exp\left(\frac{qV}{\eta_b kT}\right) - 1 \right] + PJ_{p0} \left[ \exp\left(\frac{qV}{\eta_p kT}\right) - 1 \right]. \tag{1}$$

In Eq. (1), A is the diode area,  $J_{b0}$  is the bulk saturation current density (in A/cm<sup>2</sup>),  $\eta_b$  is the bulk ideality factor, P is the perimeter of the diode,  $J_{p0}$  is the perimeter saturation current density (in A/cm),  $\eta_p$  is the perimeter ideality factor, and V is the applied voltage. Dividing the resultant equation by the area results in the following:

$$J = J_{b0} \left[ \exp \left( \frac{qV}{\eta_b kT} \right) - 1 \right] + \frac{P}{A} J_{p0} \left[ \exp \left( \frac{qV}{\eta_p kT} \right) - 1 \right]. \tag{2}$$

Thus, for a given voltage, if the measured current density is plotted as function of the perimeter to area ratio, a straight line should be obtained with the slope given by the perimeter current component and the x intercept given by the bulk current component. If the measurement is performed at two different voltages between which the ideality factor is assumed to be constant, then two values of slopes can be obtained as shown in the following:

slope

$$1 = J_{p0} \left[ \exp \left( \frac{qV_1}{\eta_p kT} \right) - 1 \right],$$

(3)

slope

$$2 = J_{p0} \left[ \exp \left( \frac{q V_2}{\eta_p k T} \right) - 1 \right].$$

(4)

The above two equations can be solved simultaneously to obtain the values of  $J_{p0}$  and  $\eta_p$ . This technique has been applied on GaAs diodes and solar cells to study the effect of perimeter recombination.<sup>12</sup> The bulk current components can be obtained by dividing Eq. (1) by the perimeter to obtain

$$\frac{I}{P} = \frac{A}{P} J_{b0} \left[ \exp\left(\frac{qV}{\eta_p kT}\right) - 1 \right] + J_{p0} \left[ \exp\left(\frac{qV}{\eta_p kT}\right) - 1 \right]. \quad (5)$$

Thus the bulk current components can be obtained from the slope of the least-squares fit of an I/P vs A/P plot. Taking the data at two different voltages allows for the extraction of  $J_{b0}$  and  $\eta_b$ , which characterize the bulk current component.

# **III. DEVICE FABRICATION**

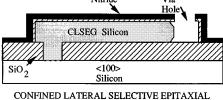

Five different  $p^+/n$  diode structures were fabricated in this study. Two were used as a reference and the other three were the SEG diodes under investigation.

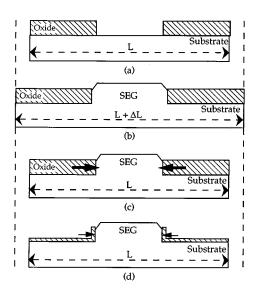

## A. Process 1

The first reference diode (process 1) was a conventional recessed local oxidation of silicon (LOCOS) isolation sidewall oxide diode in n-type,  $1-5~\Omega$  cm,  $\{100\}$  substrate. A photoresist mask was used to etch through a nitride, pad oxide, and  $0.5~\mu$ m of silicon using reactive ion etching (RIE). The  $0.8~\mu$ m LOCOS oxide was then grown, the nitride and pad oxide removed, and the wafer front was implanted with boron to form the  $p^+$  diode and the wafer back was implanted with arsenic to form the back contact. The implants were activated by a  $1000~^{\circ}$ C wet oxidation resulting in  $0.12~\mu$ m oxide on the diode. Contacts were opened and devices were metalized with approximately  $0.25~\mu$ m of Al-1% Si alloy which was defined using lift-off. The wafers were annealed at  $415~^{\circ}$ C in dry  $N_2$  for 20 min. The final cross section of the two reference diodes is shown in Fig. 2(a).

## B. Process 2

This diode structure also served as a reference. The fabrication process started with n-type,  $1-5~\Omega$  cm,  $\{100\}$  silicon wafers. Boron was implanted in the entire front for  $p^+$  diode formation and the back of the wafer was implanted with arsenic. A photoresist mask was then used to anisotropically etch through 2  $\mu$ m of silicon using Freon 115 gas. The implants were activated and contacts were formed similar to the diode of process 1. The final cross section is shown in Fig. 2(b). Using process 2, the reactive-ion-etched sidewall can be examined and can be compared with the LOCOS and other SEG sidewall diodes.

#### C. Process 3

Process 3 was a diode structure with the SEG oxide side-wall interface of interest. The fabrication process started with n-type  $1-5~\Omega$  cm,  $\{100\}$  silicon wafers. The device structures were oriented along the  $\langle 100 \rangle$  direction on the  $\{100\}$  plane to reduce perimeter defects and enhance the material quality. The process began by growing a 1.2  $\mu$ m of field oxide on the silicon. A positive photoresist mask was then used to wet etch the oxide. SEG/ELO of silicon was performed in a reduced-pressure pancake-type rf-heated epitaxial reactor. A 5 min hydrogen bake and 30 s HCl etch, both at 970 °C, were used prior to growth. SEG/ELO was then started from the silicon seed holes at 970 °C and 40 Torr at a growth rate of  $\approx 0.10~\mu$ m/min to result in 2.5  $\mu$ m of growth. The growth

Fig. 2. The two reference diode structures. (a) Recessed LOCOS isolated diode structure, process 1, (b) RIE sidewall diode, process 2, (c) wet-etched oxide SEG diode, process 3, (d) RIE oxide SEG diode, process 4.

did result in silicon material over the field oxide. The wafer was chemical-mechanically polished (CMP) down to the top surface using the field oxide as an etch stop. All of the overgrowth was removed and a planar surface was obtained. After the CMP, a  $p^+$  diode was formed and the fabrication proceeded exactly as in processes 1 and 2. The final cross section of the diode is shown in Fig. 2(c).

# D. Process 4

Process 4 was a diode structure fabricated identical to that of process 3 except that fact that the oxide was anisotropically RIE using CHF<sub>3</sub> and O<sub>2</sub>. A dry oxidation at 1000 °C for 20 min was performed to anneal the RIE damage. The resultant oxide was etched using BHF (buffered hydroflouric

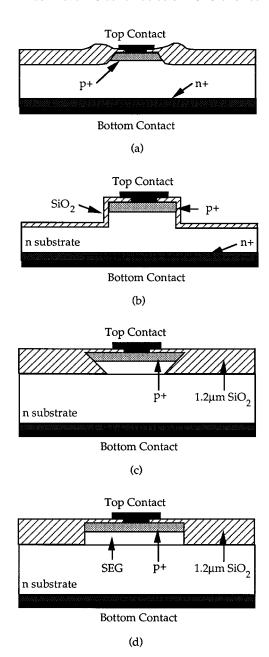

Fig. 3. Process flow of the thin oxide cavity SEG diode, process 5.

acid). The rest of the processing including the SEG was identical to the earlier process. The structure of process 4 is also an ideal candidate for a facet-free isolation technology using SEG and chemical-mechanical polishing. <sup>13,14</sup> The final cross section of the diode is shown in Fig. 2(d).

## E. Process 5

Process 5 consisted of a unique structure having only a 0.3  $\mu$ m oxide sidewall before the SEG was performed. The motive behind fabricating this process was to examine the effect of sidewall oxide thickness before the SEG. The fabrication process started with n-type,  $1-5~\Omega$  cm,  $\{100\}$  silicon wafers. The device structures were oriented along the  $\langle 100 \rangle$  direction on the  $\{100\}$  plane to reduce perimeter defects and enhance the material quality. The process began by growing an 800 Å thick pad oxide followed by a 0.25  $\mu$ m Si $_3$ N $_4$  deposition at 800 °C. A photoresist mask was used to anisotropically etch through the Si $_3$ N $_4$  in a RIE using SF $_6$ . The oxide was then etched using Freon 115. Following the oxide etch, 1  $\mu$ m of the silicon was anisotropically etched in Freon 115 plasma as shown in Fig. 3(a). The photoresist mask was then removed and the wafers were oxidized at 1050 °C to

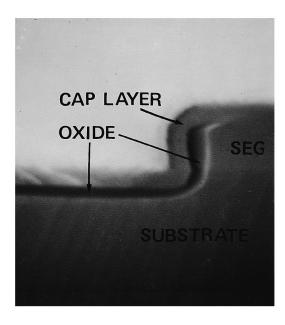

Fig. 4. SEM showing the final cross section of the thin oxide cavity SEG diode.

form an oxide 0.5  $\mu$ m thick, as shown in Fig. 3(b). The nitride and pad oxide were then removed during which the oxide on the substrate was reduced to 0.30  $\mu$ m. The silicon in the active areas was now exposed. The single crystal silicon was etched down to the substrate level using a mixture of 47 g KOH, 127 ml H<sub>2</sub>O, and 39 ml isopropanol. Next, SEG was performed similar to the last two processes. Silicon did not grow out and over the thin oxide and the planarization step was not used. Following the SEG, the diode formation was the same as described for the previous diodes. The final cross section is shown in Fig. 3(d). The thin oxide wall is about 1.2  $\mu$ m high and 0.3  $\mu$ m wide as shown in the cross-sectional SEM in Fig. 4. SEG was grown in the region bounded by the thin sidewall.

#### IV. CHARACTERIZATION RESULTS

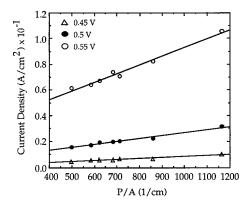

The electrical characterization of the sidewall and bulk was performed by the method described earlier. The current through the diode was measured at three different voltages of 0.425, 0.45, and 0.475 V, where the ideality factor was constant. The measured current was divided by the area and the current density obtained was plotted versus the P/A ratio. The least-squares fit of the data was used to obtain the sidewall parameters  $\eta_p$  and  $J_{p0}$ . Figure 5 shows one representative J vs P/A plot. To obtain the bulk parameters  $\eta_b$  and  $J_{b0}$  for the diodes, I/P was plotted as a function of A/P. The bulk parameters will include the contribution from all defects except the ones at the sidewall interface. Twenty devices are measured and the average values of parameters are listed in Table I.

Process 1 shows excellent bulk and sidewall parameters indicating almost no recombination in the silicon-controlled rectifier (SCR) region. Process 2 diodes show an ideality factor of 1.1 which could be due to the presence of RIE damage along the sidewall not completely removed by the oxidation. The sidewall ideality factor is slightly higher than

Fig. 5. A representative current density vs perimeter to area ratio plot.

the LOCOS and indicates a lower quality sidewall. The reverse leakage was measured so that the depletion region would not go into the substrate. Process 3 shows a higher ideality factor of 1.37 for the sidewall and 1.32 for the bulk. This indicates the presence of defects along and close to the SEG sidewall. The ideality factor at 0.45 V for processes 3 and 4, 1.29 and 1.23, respectively, are very close; however, the perimeter and bulk parameters are different. The RIE perimeter values are higher than the wet-etched oxide process. This could be due to that rough oxide sidewall due to the RIE.

The thin oxide cavity SEG diode (process 5) showed the most interesting results. The ideality factors were close to the values of processes 1 and 2 even though they had the selective epitaxial growth sidewall interface. The low ideality factors can be attributed to the thin sidewall oxide. If the defects are generated due to thermal stress during the cool-down period after the SEG growth, then the SEG Si grown in this structure will experience the minimum thermal stress due to the presence of the thin oxide which is free to expand and contract. Also, the corner of the substrate/SEG intersection will experience the least thermal stress due to the thin oxide present there.

Transmission electron microscopy was also performed on the three SEG diodes, from processes 3, 4, and 5, to examine the sidewall defects on samples which were not planarized. No defects were observed in the samples close to the sidewall and bulk. If the thermal stress is the main cause of the SEG sidewall defects, then the SEG in these diodes can be

TABLE I. Summary of results.

| Device            | $\eta$ at 0.45 | $\eta_p$ | $J_{p0}$ (A/cm)        | $oldsymbol{\eta}_b$ | $J_{b0}$ (A/cm <sup>2</sup> ) | $J_{\rm rev}$ (A/cm <sup>2</sup> ) |

|-------------------|----------------|----------|------------------------|---------------------|-------------------------------|------------------------------------|

| Sample 1          |                |          |                        |                     |                               | $2.31 \times 10^{-7}$              |

| (LOCOS)           | 1.02           | 1.00     | $4.35 \times 10^{-14}$ | 1.05                | $4.04 \times 10^{-11}$        | at −2 V                            |

| Sample 2          |                |          |                        |                     |                               | $2.03\times10^{-7}$                |

| (RIE substrate)   | 1.10           | 1.15     | $8.05 \times 10^{-13}$ | 1.05                | $8.21 \times 10^{-11}$        | at −2 V                            |

| Sample 3          |                |          |                        |                     |                               | $2.88 \times 10^{-7}$              |

| (wet-etch oxide)  | 1.29           | 1.37     | $1.56 \times 10^{-11}$ | 1.32                | $6.78 \times 10^{-9}$         | at −1 V                            |

| Sample 4          |                |          |                        |                     |                               | $4.00\times10^{-7}$                |

| (RIE oxide)       | 1.23           | 1.49     | $4.17 \times 10^{-11}$ | 1.09                | $3.59 \times 10^{-10}$        | at −1 V                            |

| Sample 5          |                |          |                        |                     |                               | $4.97 \times 10^{-7}$              |

| (thin oxide wall) | 1.15           | 1.21     | $3.79 \times 10^{-12}$ | 1.08                | $1.91 \times 10^{-10}$        | at −1 V                            |

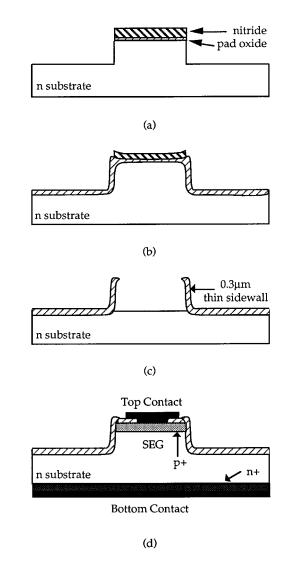

Fig. 6. Schematic showing the compressive forces on the SEG sidewall during the cool-down period, (a) before the SEG, (b) after the SEG with the wafer in the expanded state, (c) after the cool-down period, (d) the thin oxide sidewall cavity wafer after the cool-down period.

postulated to be strained but not enough to cause plastic deformation resulting in dislocations. The thermal stress and strain could cause traps in the energy gap, resulting in a higher recombination and hence a slightly higher ideality factor but not enough to cause plastic deformation.

## V. DISCUSSION

The results described above can be explained by taking into account the thermal stress generated at the SEG sidewall. As the temperature is ramped up before the growth, there is an increase in the volume of the oxide and the silicon substrate according to their respective coefficients of thermal expansion,  $\alpha$ , which is a function of temperature. At 970 °C,  $\alpha_{\rm Si}$  and  $\alpha_{\rm ox}$  are approximately  $3.9\times10^{-6}/\,^{\circ}{\rm C}$  and  $0.5 \times 10^{-6}$  °C, respectively. The silicon substrate plays a very important role in determining the stress at the SEG sidewall. It will expand more in the horizontal direction than along its thickness and about 5-8 times more than the oxide. SEG Si is grown at the high temperature, when the substrate is in the expanded state. During the cool-down period the substrate will contract back and force the oxide, which is bonded to the substrate, to apply a compressive stress on the SEG. As shown in Fig. 6, for processes 3 and 4 the entire field oxide is being contracted along with the substrate, whereas, for process 5, the oxide exerting the force is only 0.3  $\mu$ m wide. The stress applied is not large enough to cause plastic deformation in all three structures.

# VI. CONCLUSIONS

This article presented an extensive characterization of the sidewall defects in high quality selective epitaxial growth (SEG) of silicon with an oxide sidewall. The unusual interface of SEG with the sidewall oxide is prone to defects, the major cause being thermal stress generated in the cool-down period after the SEG. The experiments in this study proved that the sidewall oxide width, determining the thermal stress, plays a major role in determining the SEG sidewall material quality. Diodes were fabricated and electrically characterized to show that the thin oxide cavity SEG diode (process 5) exhibited the lowest ideality factors and saturation current density as compared to thick oxide cavity SEG diodes (Processes 3 and 4). A lower growth temperature would further reduce the thermal stress and improve the sidewall SEG material quality.

## **ACKNOWLEDGMENTS**

The authors would like to thank A. Kabir and J. Pak for help in KOH etching and G. Yeric and K. Wu of U. T. Austin for oxide etching. The work was supported by the Semiconductor Research Corporation under Contract No. 95-SJ-108.

- <sup>1</sup>G. W. Neudeck, P. J. Schuberts, J. L. Glenn, Jr., J. A. Friedrich, W. A. Klaasan, R. P. Zingg, and J. P. Denton, J. Electron. Mater. **19**, 1111 (1990).

- <sup>2</sup>L. Jastrzebski, J. Cryst. Growth **63**, 493 (1983).

- <sup>3</sup>R. Zingg, J. A. Friedrich, G. W. Neudeck, and B. Hoefflinger, IEEE Trans. Electron Devices **37**, 1452 (1990).

- <sup>4</sup>R. Bashir, S. Venkatesan, G. W. Neudeck, and J. P. Denton, IEEE Electron Device Lett. 13, 392 (1992).

- <sup>5</sup>J. Borland, M. Gangani, R. Wise, S. Fong, Y. Oka, and Y. Matsumoto, Solid State Technol. 111 (1988).

- <sup>6</sup>H. M. Liaw, and G. J. Seiter, in Proceedings of the 10th International Conference on Chemical Vapor Deposition, 1987 (unpublished), p. 317.

- <sup>7</sup>J. Glenn, Jr., and G. W. Neudeck, Electron. Lett. **26**, 1677 (1990).

- <sup>8</sup>A. Ishitani, H. Kitajima, N. Endo, and N. Kasai, Jpn. J. Appl. Phys. 28, 841 (1989).

- <sup>9</sup>W. A. Klassen, and G. W. Neudeck, IEEE Trans. Electron Devices 37, 273 (1990).

- <sup>10</sup>J. T. McGinn, L. Jastrzebski, and J. F. Corboy, J. Electrochem. Soc. 131, 398 (1984).

- <sup>11</sup>D. Thebault and L. Jastrzebski, RCA Rev. **41**, 593 (1980).

- <sup>12</sup>P. E. Dodd, T. B. Stellweg, M. R. Malloch, and M. S. Lundstrom, IEEE Trans. Electron Devices 38, 1253 (1991).

- <sup>13</sup>H. Kurtan, H. J. Voss, W. Kim, and W. L. Engl., IEEE Trans. Electron Devices ED-30, 1511 (1983).

- <sup>14</sup>N. Endo, K. Tanno, A. Ishitani, Y. Kurogi, and H. Tsuya, IEEE Trans. Electron Devices ED-31, 1283 (1984).